[AMBA] AXI Protocol 정리 (1) | 아키텍쳐 구조, 핸드쉐이크, 채널 | write / read channel, signal, architecture, handshake

2024. 5. 6. 21:15ㆍAMBA

반응형

ARM에서 제공하는 AXI Spec 문서를 번역하며 정리함.

AXI protocol

- High-bandwidth (고대역폭) 와 low-latency (저지연) 설계에 적합

- 복잡한 bridge 사용없이 고주파수 동작을 제공

- 광범위의 구성요소 인터페이스 요구사항을 충족

- 초기 액세스 지연시간이 긴 메모리 컨트롤러에 적합

- 상호 연결 아키텍처 구현에 유연성을 제공

- 기존 AHB, APB 인터페이스와 호환이 가능 (backward-compatible)

AXI protocol의 특징

- Address / control 그리고 data 단계를 구분

- byte strobe을 사용하여 unaligned (정렬되지않은) data transfer를 지원

- 오직 발행된 start address만 사용하여 burst-based transaction을 사용

- 구분된 read / write data channel은 low-cost Direct Memory Access (DMA)를 제공

- 다수의 outstanding address를 지원

- out-of-order transactio completion을 지원

- timing closure를 제공하기 위해 레지스터 단계를 쉽게 추가 가능

AXI Architecture

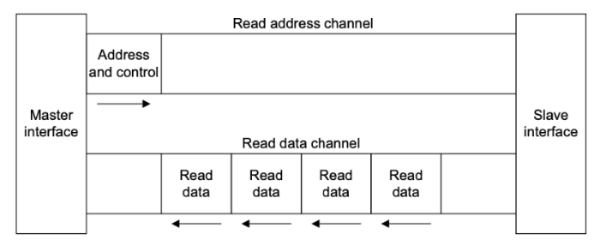

AXI protocol 은 독립된 다섯 개의 채널이 있다.

- AR : Read address

- R : Read data

- AW : Write address

- W : Write data

- B : Write response

A가 붙어 있으면 Address, A 없이 나온 것은 그냥 data channel.

read response 신호가 없는 이유는 다음에 설명

1. Write Channel

- AWADDR : write burst transaction에서 첫 번째로 전송될 주소를 전송하는 신호. (Master -> Slave)

- AWVALID : 채널의 유효한 write address와 control information 전송을 알리는 신호. (Master -> Slave)

- AWREADY : Slave가 address와 control 신호를 받아들일 준비가 됐다는 것을 알리는 신호. (Slave -> Master)

- WDATA : Write data 신호. (Master -> Slave)

- WLAST : Write burst에서의 마지막 전송을 알리는 신호. (Master -> Slave)

- WVALID : 유효한 write data와 strobe를 사용할 수 있다는 것을 알리는 신호입니다. (Master -> Slave)

- WREADY : Slave가 write data를 받아들일 준비가 됐다는 신호.

- BRESP : Write transaction의 상태를 나타내는 (response) 신호. (Slave -> Master)

- BVALID : 채널의 유효한 Write response 전송을 알리는 신호. (Slave -> Master)

- BREADY : Master가 Write response를 받아들일 수 있다는 것을 알리는 신호입니다. (Master -> Slave)

2. Read Channel

- ARADDR : Read burst transaction의 첫 번째 주소를 전송하는 신호. (Master -> Slave)

- ARVALID : 채널의 유효한 read address와 control information의 전송을 알리는 신호. (Master -> Slave)

- ARREADY : Slave가 address와 control 신호를 받아들일 준비가 됐다는 것을 알리는 신호. (Slave -> Master)

- RDATA : Read data 신호. (Slave -> Master)

- RLAST : read burst에서 마지막 전송을 나타내는 신호. (Slave -> Master)

- RVALID : 요구된 read data의 전송을 알리는 신호. (Slave -> Master)

- RREADY : Master가 read data와 response information을 받아들일 수 있음을 나타내는 신호. (Master -> Slave)

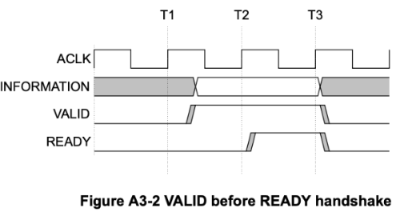

Handshake process

AW, W, AR, R, B 이와 같은 5개의 transaction channel은 모두 동일한 VALID/READY handshake process를 사용하여 address/data/control 정보를 전송한다. 이러한 two-wat flow control nachanism은 master와 slave가 서로 간에 이동하는 속도를 제어할 수 있음을 의미한다.

- VALID 신호 : source가 destination에게 address, data, control information을 언제 사용할 수 있는지에 대해 물어보는 signal

- READY 신호 : destination이 source에게 정보를 받아들일 수 있음을 나타내는 signal

전송은 오직 VALID와 READY 신호가 모두 HIGH 일 때 발생한다.

master 및 slave 인터페이스에는 input 신호와 output 신호사이에 combinatorial path가 있어서는 안 된다.

- dest에서 데이터를 받을 때 READY를 1로 띄운다

- src는 dest로부터 입력되는 READY신호가 1이고, 자신이 출력하는 VALID가 1일 때, 해당 주기(Period)에서 데이터 전송됐음을 알게 된다

- 중요한 점은 VALID=1, READY=1인 구간에서 데이터 트랜잭션이 이뤄진다는 점이며, 구현시 VALID나 READY를 먼저 띄우는 방식이나 또는 동시에 띄우는 방식은 문제가 되지 않는다.

- AXI의 VALID/READY 핸드셰이크는 다음과 같이 세 가지 방식으로 구현될 수 있다

방식 1 ) 그림 A3-2은 READY전에 VALID가 발생한 경우이다.

- 소스는 T1 이후에 주소, 데이터 또는 제어 정보를 제공하고 VALID 신호를 assert 한다.

- 목적지는 T2 이후에 READY 신호를 assert 하고, 소스는 이 주장이 인식될 때 T3에서 transfer가 발생할 때까지 정보를 안정적으로 유지해야 한다.

방식 2) 그림 A3-3은 VALID 전에 READY가 발생한 경우이다.

- 목적지는 주소, 데이터 또는 제어 정보가 유효하기 전에 T1 이후로 READY를 assert 하여 정보를 받아들일 수 있음을 나타낸다.

- 소스는 정보를 제시하고 T2 이후에 VALID를 assert 하고, 이것을 인식하면 T3에서 transfer가 발생한다.

이 경우 trasfer가 단 한 클럭만에 발생했음을 의미한다.

방식 3) 그림 A3-4은 VALID와 READY가 같이 발생한 경우이다.

- 소스와 목적지 모두 T1 이후에 주소, 데이터 또는 제어 정보를 전송할 수 있음을 나타낸다.

- 이 경우 전송은 VALID와 READY의 assert가 모두 인식될 때 상승 클록 에지에서 발생한다.

이 경우 transfer가 T2에서 발생한다는 것을 의미한다.

반응형